**AK4499**

## = Preliminary =

# Premium Switched Resistor 4ch DAC

#### 1. General Description

The AK4499 is a 32-bit 4ch Switched Resistor DAC which adopts newly developed technology, achieving the industry's leading level low distortion and low noise characteristics. It corresponds to a 768kHz PCM input and an DSD512 input at maximum, suitable for playback of high resolution audio sources that are becoming widespread in Network Audio and USB-DACs Audio systems. In addition, it is capable of supporting a wide range of signals and achieving low out-of-band noise. The AK4499 has six types of 32-bit digital filters, realizing simple and flexible sound reproduction in wide range of applications.

#### 2. Features

- 4-ch Switched Resistor DAC

- THD+N: -124 dB

- Dynamic Range, S/N: 140 dB (Mono), 137 dB (Stereo), 134 dB (4ch)

- 128x Over Sampling

- Sampling Rate: 8 kHz ~ 768 kHz

- 32-bit 8x Digital Filter Short Delay Sharp Roll-off, GD = 6.0/fs Short Delay Slow Roll-off, GD = 5.0/fs Sharp Roll-off Slow Roll-off Super Slow Roll-off Low Dispersion Short Delay Filter

- DSD64, DSD128, DSD256, DSD512 Input Support Filter1 (fc = 37 kHz, DSD64 mode)

Filter2 (fc = 65 kHz, DSD64 mode)

- Digital De-emphasis for 32, 44.1 and 48kHz sampling

- Soft Mute

- Digital Attenuator (0 dB ~ -127 dB, 0.5 dB step + mute)

- Mono Mode

- External Digital Filter Interface (EXDF Mode)

- PCM/DSD, EXDF/DSD Mode Automatic Mode Switching Function

- Audio I/F Format

- MSB Justified

- LSB Justified

- I<sup>2</sup>S

- DSD

- TDM

- Daisy Chain

- Master Clock

- fs = 8 kHz ~ 32 kHz: 256fs, 384fs, 512fs, 768fs, 1152fs

- fs = 32 kHz ~ 54 kHz: 256fs, 384fs, 512fs, 768fs

- fs = 54 kHz ~ 108 kHz: 256fs, 384fs

- fs = 108 kHz ~ 216 kHz: 128fs, 192fs

- fs = 384 kHz : 32fs, 48fs, 64fs, 96fs

- fs = 768 kHz : 16fs, 32fs, 48fs, 64fs

- Register Control Mode with 3-wire Serial or I<sup>2</sup>C interface

- Pin Control Mode

- Power Supply: Internal LDO (LDOE pin = "H"); TVDD = 3.0 ~ 3.6 V, AVDD = 4.75 ~ 5.25 V, VDDL1/R1/L2/R2 = 4.75 ~ 5.25 V

External Supply (LDOE pin = "L"); TVDD = 1.7 ~ 3.6 V, DVDD = 1.7 ~ 1.98 V,

- AVDD = 4.75 ~ 5.25 V, VDDL1/R1/L2/R2 = 4.75 ~ 5.25 V

- Operational Temperature: -40 ~ 85 °C

- Digital Input Level: CMOS

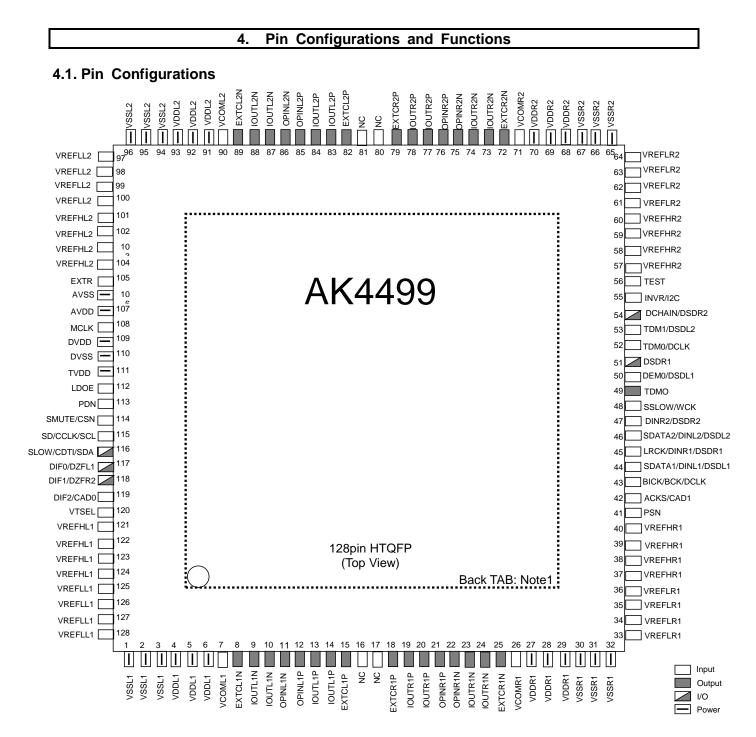

- Package: 128-pin HTQFP

#### 3. Block Diagram and Functions

#### 3.1. Block Diagram

Figure 1. AK4499 Block Diagram

#### 3.2. Functions

| Block                 | Function                                                                                                                                                                     |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCM Data Interface    | Execute serial/parallel conversion of SDATA1/2 input data by synchronizing with LRCK and BICK, and generate TDM output data.                                                 |

| External DF Interface | Receive external digital filter outputs. Execute serial/parallel conversion of DINL1/2 and DINR1/2 input data by synchronizing with BICK.                                    |

| DSD Data Interface    | 1-bit data that is input from DSDL1/2 and DSDR1/2 pins is received by synchronizing with DCLK.                                                                               |

| DSD Filter            | FIR filter that reduces high frequency noise of DSD input data                                                                                                               |

| DATT, Soft Mute       | Apply DATT and Soft Mute process to input data.                                                                                                                              |

| De-emphasis &         | A digital filter that applies De-emphasis process to input data and executes                                                                                                 |

| Interpolator          | over sampling.                                                                                                                                                               |

| ΔΣ Modulator          | Output multi-bit data to SR DAC. This block consists of a third-order digital delta-sigma modulator.                                                                         |

| SR DAC                | Convert multi bit output of $\Delta\Sigma$ Modulator into analog signal. This block consists of a switched resistor DAC.                                                     |

| Control Register      | Keep register settings for each mode. Control registers are accessed in 3-wire (CSN, CCLK, CDTI) or I2C-Bus (SCL, SDA) control mode.                                         |

| Clock Divider         | Divide Master Clock<br>In PCM mode, master clock is divided automatically by fs rate auto detection<br>function. In DSD mode, the master clock frequency is set by DCKS bit. |

| MCLK Stop Detection   | Detects when the master clock input is absent.                                                                                                                               |

| IREF                  | Generate reference current from the reference voltage generated internally, using an external resistor.                                                                      |

| LDO                   | Generate power for internal digital circuit (1.8V typ.).                                                                                                                     |

Note 1: The exposed pad on the bottom surface of the package must be connected to ground (AVSS).

#### 4.2. Functions

| No.                | Pin Name       | I/O | Function                                                                                                                                              | Power Down<br>State                         |

|--------------------|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 1-3                | VSSL1          | -   | L1ch Analog Ground pin.                                                                                                                               | -                                           |

| 4-6                | VDDL1          | -   | L1ch Analog Power Supply pin.                                                                                                                         | _                                           |

| 7                  | VCOML1         | 1   | L1ch VCOM pin. VCOML1 is connected to the midpoint of resistors between VREFHL1 and VREFL1.                                                           | Hi-Z                                        |

| 8                  | EXTCL1N        | 0   | External Capacitor connection pin. This pin should be connected to 1 $\mu$ F to VSSL1.                                                                | Pull-down to<br>VSSL1<br>(250 kΩ, typ)      |

| 9,10               | IOUTL1N        | 0   | Current Output pin (L1ch Negative Signal).                                                                                                            | Connected to<br>OPINL1N<br>(64 Ω, typ)      |

| 11                 | OPINL1N        | 0   | Common Voltage Input pin (L1ch Negative Signal).                                                                                                      | Connected to<br>IOUTL1N<br>(64 Ω, typ)      |

| 12                 | OPINL1P        | 0   | Common Voltage Input pin (L1ch Positive Signal).                                                                                                      | Connected to<br>IOUTL1P<br>(64 Ω, typ)      |

| 13,14              | IOUTL1P        | 0   | Current Output pin (L1ch Positive Signal).                                                                                                            | Connected to<br>OPINL1P<br>(64 Ω, typ)      |

| 15                 | EXTCL1P        | 0   | External Capacitor connection pin. This pin should be connected to 1 $\mu$ F to VSSL1.                                                                | Pull-down to<br>VSSL1<br>(250 kΩ, typ)      |

| 16,17              | NC             | -   | No internal bonding. Connect to AVSS.                                                                                                                 | -                                           |

| 18                 | EXTCR1P        | 0   | External Capacitor connection pin. This pin should be connected to 1 $\mu$ F to VSSR1.                                                                | Pull-down to<br>VSSR1<br>(250 kΩ, typ)      |

| 19,20              | IOUTR1P        | 0   | Current Output pin (R1ch positive signal).                                                                                                            | Connected to<br>OPINR1P<br>(64 Ω, typ)      |

| 21                 | OPINR1P        | 0   | Common Voltage input pin (R1ch positive signal).                                                                                                      | Connected to<br>IOUTR1P<br>(64 Ω, typ)      |

| 22                 | OPINR1N        | ο   | Common Voltage input pin (R1ch negative signal).                                                                                                      | Connected to<br>IOUTR1N<br>(64 Ω, typ)      |

| 23,24              | IOUTR1N        | 0   | Current Output pin (R1ch negative signal).                                                                                                            | Connected to<br>OPINR1N<br>(64 Ω, typ)      |

| 25                 | EXTCR1N        | 0   | External Capacitor connection pin. This pin should be connected to 1 $\mu$ F to VSSR1.                                                                | Pull-down to<br>VSSR1<br>(250 kΩ, typ)      |

| 26                 | VCOMR1         | 1   | R1ch VCOM pin. VCOMR1 is connected to the midpoint of resistors between VREFHR1 and VREFLR1.                                                          | Hi-Z                                        |

| 27-29              | VDDR1          | -   | R1ch Analog Power Supply pin.                                                                                                                         | -                                           |

| 30-32              | VSSR1          | -   | R1ch Analog Ground pin.                                                                                                                               | -                                           |

| 33-36              | VREFLR1        |     | R1ch Low Level Reference Voltage Input pin.                                                                                                           | Hi-Z                                        |

| <u>37-40</u><br>41 | VREFHR1<br>PSN |     | R1ch High Level Reference Voltage Input pin.<br>Control Mode Select pin (Internal pull-up pin)<br>"L": Register Control mode<br>"H": Pin Control mode | Hi-Z<br>Pull-Up to<br>TVDD<br>(100 kΩ, typ) |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | No. | Pin Name | I/O | Function                                                                                               | Power Down<br>State |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|--------------------------------------------------------------------------------------------------------|---------------------|

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42  | ACKS     | I   | "L": Fixed Speed mode<br>"H": Auto Setting mode                                                        | Hi-Z                |

| 43       BCK       I       Audio Serial Data Clock pin in EXDF mode       Hi-Z         0CLK       I       DSD Clock Pin in DSD mode (@DSDPATH bit = "1")       Hi-Z         44       DINL1       I       Audio Serial Data Input pin in PCM mode       Hi-Z         44       DSDL1       I       Audio Serial Data Input pin in DSD mode       Hi-Z         45       DSDL1       I       Audio Serial Data Input pin in DSD mode       Hi-Z         45       DINR1       I       Audio Serial Data Input pin in DSD mode       Hi-Z         46       DINR1       I       Audio Serial Data Input pin in EXDF mode       Hi-Z         47       DSDR1       I       Audio Serial Data Input pin in EXDF mode       Hi-Z         48       DINR2       I       Audio Serial Data Input pin in EXDF mode       Hi-Z         47       DSDR2       I       Audio Serial Data Input pin in EXDF mode       Hi-Z         48       SSLOW       I       Digital Filter Select pin in Pin Control mode       Hi-Z         49       TDMO       O       Audio Serial Data Input pin in DSD mode       Hi-Z         50       DSDL1       I       Audio Serial Data Input pin in DSD mode                                                                                                                                                                                                                       |     | CAD1     |     | Chip Address 1 pin in Register Control mode                                                            |                     |

| DCLK       I       DSD Clock Pin in DSD mode (@DSDPATH bit = "1")         44       DINL1       I       Audio Serial Data Input pin in PCM mode       Hi-Z         44       DINL1       I       Audio Serial Data Input pin in DSD mode       Hi-Z         45       DSDL1       I       (@DSDPATH bit = "1")       Hi-Z         45       DSR1       I       Audio Serial Data Input pin in PCM mode       Hi-Z         46       DINR1       I       Audio Serial Data Input pin in DSD mode       Hi-Z         47       DSDL2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         47       DSDR2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         48       SLOW       I       Digta Filter Select pin in Pin Control mode       Hi-Z         47       DSDR2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         48       SLOW       I       Digtal Filter Select pin in Pin Control mode       Hi-Z         49       TDMO       Q       Audio Serial Data Input pin in DSD mode       Hi-Z         50       DSDL1       I       Audio Serial Data Input pin in DSD mode       Hi-Z                                                                                                                                                                                                                                             |     | BICK     |     | Audio Serial Data Clock pin in PCM mode                                                                |                     |

| SDATA1       I       Audio Serial Data Input pin in PCM mode         44       DINL1       I       Audio Serial Data Input pin in EXDF mode       Hi-Z         DSDL1       I       Audio Serial Data Input pin in DSD mode       Hi-Z         45       DINR1       I       Audio Serial Data Input pin in EXDF mode       Hi-Z         46       DSDR1       I       Audio Serial Data Input pin in DSD mode       Hi-Z         46       DSDL2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         47       SDATA2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         48       DINR2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         47       DSDR2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         48       SSLOW       I       Digital Filter Select pin in Pin Control mode       Hi-Z         49       TDMO       O       Audio Serial Data Input pin in DSD mode       Hi-Z         50       DSDL1       I       Deemphasis Enable pin in Pin Control mode       Hi-Z         51       DSDR1       I       Deemphasis Enable pin in DSD mode       Hi-Z <td< td=""><td>43</td><td>BCK</td><td>I</td><td>Audio Serial Data Clock pin in EXDF mode</td><td>Hi-Z</td></td<>                                                                                                                        | 43  | BCK      | I   | Audio Serial Data Clock pin in EXDF mode                                                               | Hi-Z                |

| 44   DINL1   I   Audio Serial Data Input pin in EXDF mode   Hi-Z     35   DSDL1   I   Audio Serial Data Input pin in DSD mode   Hi-Z     45   LRCK   I   Input Channel Clock pin in PCM mode   Hi-Z     46   DINR1   I   Audio Serial Data Input pin in EXDF mode   Hi-Z     66   DSDR1   I   Audio Serial Data Input pin in DSD mode   Hi-Z     67   DSDR12   I   Audio Serial Data Input pin in DSD mode   Hi-Z     68   DINL2   I   Audio Serial Data Input pin in DSD mode   Hi-Z     70   DSDR2   I   Audio Serial Data Input pin in DSD mode   Hi-Z     47   DSDR2   I   Audio Serial Data Input pin in DSD mode   Hi-Z     48   SSLOW   I   Digital Filter Select pin in Din Control mode   Hi-Z     49   TDMO   O   Audio Serial Data Input pin in DSD mode   HI-Z     50   DSDL1   I   De-emphasis Enable pin in Pin Control mode   HI-Z     51   DSDR1   I   Audio Serial Data Input pin in DSD mode   HI-Z     52   TDMO   O   Audio Serial Data Input pin in DSD mode   HI-Z     53   DSDL1   I   De-emphasis Enable pin in Pin control mode   HI-Z </td <td></td> <td>DCLK</td> <td>I</td> <td>DSD Clock Pin in DSD mode (@DSDPATH bit = "1")</td> <td></td>                                                                                                                                                                                                                       |     | DCLK     | I   | DSD Clock Pin in DSD mode (@DSDPATH bit = "1")                                                         |                     |

| 44       DSDL1       I       Audio Serial Data Input pin in DSD mode       Hi-Z         45       DINR1       I       Input Channel Clock pin in PCM mode       Hi-Z         46       DINR1       I       Audio Serial Data Input pin in DSD mode       Hi-Z         46       SDATA2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         46       DINL2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         47       DSDL2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         48       DINR2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         47       DSDR2       I       Audio Serial Data Input pin in DSD mode       Hi-Z         48       SSLOW       I       Digital Filter Select pin in Pin Control mode       Hi-Z         49       TDMO       O       Audio Serial Data Input pin in DSD mode       Hi-Z         50       DSDL1       I       Decemphasis Enable pin in Pin Control mode       DVSS         51       DSDR1       I       Decemphasis Enable pin in DSD mode       Hi-Z         60       DSDL1       I       Audio Serial Data Input pin in DSD mode<                                                                                                                                                                                                                           |     | SDATA1   |     | Audio Serial Data Input pin in PCM mode                                                                |                     |

| DSDL1       I       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")         45       LRCK       I       Input Channel Clock pin in PCM mode<br>DSDR1       I         45       DINR1       I       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")       Hi-Z         46       DINL2       I       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")       Hi-Z         47       SDAT2       I       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")       Hi-Z         48       SSLOW       I       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")       Hi-Z         48       SSLOW       I       Digital Filter Select pin in DSD mode<br>(Internal pull-down pin in EXDF mode       Hi-Z         49       TDMO       O       Audio Serial Data Input pin in DSD mode<br>(Internal pull-down pin)       Pull-down to<br>DVSS<br>(100 kQ, typ)         50       DEM0       I       De-emphasis Enable pin in Pin Control mode<br>(Internal pull-down pin)       Hi-Z         51       DSDL1       I       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")       Hi-Z         52       TDMO       I       De-emphasis Enable pin in Pin control mode.<br>DCLK       Hi-Z       Hi-Z         53       DSDL1                                                                                       | 4.4 | DINL1    | I   | Audio Serial Data Input pin in EXDF mode                                                               | 11: 7               |

| 45       DINR1       I       Audio Serial Data Input pin in EXDF mode<br>(@DSDPATH bit = "1")       Hi-Z         46       DSDL2       I       Audio Serial Data Input pin in PCM mode<br>DINL2       Hi-Z       Hi-Z         46       DSDL2       I       Audio Serial Data Input pin in PCM mode<br>DINL2       Hi-Z       Hi-Z         47       DSDR2       I       Audio Serial Data Input pin in EXDF mode<br>(@DSDPATH bit = "1")       Hi-Z         48       SSLOW       I       Digital Filter Select pin in Pin Control mode<br>(Internal pull-down pin)       Hi-Z         49       TDMO       O       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")       Pull-down to<br>DVSS<br>(100 kΩ, typ)         50       DEM0       I       Degraphase Enable pin in Pin Control mode<br>(Internal pull-down pin)       Pull-down to<br>DVSS<br>(100 kΩ, typ)         51       DSD11       I       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")       Hi-Z         52       TDM0       I       De-emphasis Enable pin in Pin control mode.       Hi-Z         53       DSDL2       I       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")       Hi-Z         54       DSDL2       I       Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")       Hi-Z </td <td>44</td> <td>DSDL1</td> <td>I</td> <td></td> <td>ΠI-Z</td> | 44  | DSDL1    | I   |                                                                                                        | ΠI-Z                |

| 45   DSDR1   I   Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")   HI-2     46   DINL2   I   Audio Serial Data Input pin in PCM mode<br>DINL2   Hi-2     46   DSDL2   I   Audio Serial Data Input pin in EXDF mode<br>(@DSDPATH bit = "1")   Hi-Z     47   DINR2   I   Audio Serial Data Input pin in EXDF mode<br>(@DSDPATH bit = "1")   Hi-Z     48   SSLOW   I   Digital Filter Select pin in Pin Control mode<br>(@DSDPATH bit = "1")   Hi-Z     48   SSLOW   I   Digital Filter Select pin in Pin Control mode<br>(Internal pull-down pin)   Hi-Z     50   DEM0   I   De-emphasis Enable pin in Pin Control mode<br>(@DSDPATH bit = "0")   Hi-Z     51   DSDR1   I   Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")   Hi-Z     52   TDM0   I   De-emphasis Enable pin in Pin Control mode<br>(@DSDPATH bit = "0")   Hi-Z     52   TDM0   I   DSDR1 bit = "0")   Hi-Z     53   DSDL2   I   Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")   Hi-Z     54   DSDR2   I   Audio Serial Data Input pin in Pin control mode.   Hi-Z     54   DSDR2   I   Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")   Hi-Z     55   I2C   I <td></td> <td>LRCK</td> <td></td> <td>Input Channel Clock pin in PCM mode</td> <td></td>                                                                                                       |     | LRCK     |     | Input Channel Clock pin in PCM mode                                                                    |                     |

| DSDR1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")46DINL2IAudio Serial Data Input pin in PCM mode<br>DSDL2I47DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")Hi-Z47DINR2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")Hi-Z48SSLOWIDigital Filter Select pin in Pin Control mode<br>(Internal pull-down pin)Hi-Z48SSLOWIDigital Filter Select pin in Pin Control mode<br>(Internal pull-down pin)Hi-Z49TDMOOAudio Serial Data Input pin in DSD mode<br>(Internal pull-down pin)Pull-down to<br>DVSS<br>(100 kQ, typ)50DEM0IDe-emphasis Enable pin in Pin Control mode<br>(Internal pull-down pin)Hi-Z51DSD11IDe-emphasis Enable pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z52TDM0IDe-emphasia Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z53DSL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CIAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                  | 45  | DINR1    | I   | Audio Serial Data Input pin in EXDF mode                                                               | 11: 7               |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45  | DSDR1    | I   |                                                                                                        | ΠI-Z                |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | SDATA2   |     |                                                                                                        |                     |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46  | DINL2    | I   | Audio Serial Data Input pin in EXDF mode                                                               | Ц; 7                |

| 47DSDR2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "1")Hi-Z48SSLOWIDigital Filter Select pin in Pin Control modeHi-Z49TDMOOAudio Serial Data Output pin in EXDF modePull-down to<br>DVSS<br>(100 kΩ, typ)49TDMOOAudio Serial Data Output pin in Daisy Chain mode<br>(Internal pull-down pin)Pull-down to<br>DVSS<br>(100 kΩ, typ)50DEM0IDe-emphasis Enable pin in Pin Control modeHi-Z51DSDL1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z51DSDR1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z52TDM0ITDM Mode select 0 pin in Pin control mode.<br>DCLKHi-Z53DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CIAudio Serial Data Input Pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CISerial Control Interface Select pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                           | 40  | DSDL2    | I   |                                                                                                        | ni-2                |

| DSDR21(@DSDPATH bit = "1")48SSLOWIDigital Filter Select pin in Pin Control modeHi-Z49TDMOOAudio Serial Data Output pin in EXDF modePull-down to<br>DVSS<br>(100 kΩ, typ)49TDMOOAudio Serial Data Output pin in Daisy Chain mode<br>(Internal pull-down pin)Pull-down to<br>DVSS<br>(100 kΩ, typ)50DEM0IDe-emphasis Enable pin in Pin Control mode<br>(@DSDPATH bit = "0")Hi-Z51DSDL1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z52TDM0ITDM Mode select 0 pin in Pin control mode.<br>(@DSDPATH bit = "0")Hi-Z53DSL2ITDM Mode select 1 pin in Pin control mode.<br>(@DSDPATH bit = "0")Hi-Z54DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DSDR2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CIAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CIR1/2ch Signal Invert pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z56TESTIConnect to DVSS (Internal control interface.<br>"H": I²C Bus serial control interface.<br>"H": I²C Bus serial control interface.Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                              |     | DINR2    |     | Audio Serial Data Input pin in EXDF mode                                                               |                     |

| 48SSLOWIDigital Filter Select pin in Pin Control modeHi-Z49TDMOOAudio Serial Data Output pin in Daisy Chain mode<br>(Internal pull-down pin)Pull-down to<br>DVSS<br>(100 kΩ, typ)50DEM0IDe-emphasis Enable pin in Pin Control mode<br>(@DSDPATH bit = "0")Hi-Z51DSDR1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z51DSDR1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z52TDM0ITDM Mode select 0 pin in Pin control mode.<br>(@DSDPATH bit = "0")Hi-Z53TDM1IDSD Clock pin in DSD mode (@DSDPATH bit ="0")Hi-Z54DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DSDR2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CIDaisy Chain Mode Select pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CIR1/2ch Signal Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47  | DSDR2    | I   |                                                                                                        | Hi-Z                |

| WCKIWord Clock input pin in EXDF mode49TDMOOAudio Serial Data Output pin in Daisy Chain mode<br>(Internal pull-down pin)Pull-down to<br>DVSS<br>(100 kΩ, typ)50DEM0IDe-emphasis Enable pin in Pin Control modeHi-Z50DSDL1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z51DSDR1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z52TDM0ITDM Mode select 0 pin in Pin control mode.<br>(@DSDPATH bit = "0")Hi-Z53DSDL2IDSD Clock pin in DSD mode (@DSDPATH bit ="0")<br>(@DSDPATH bit = "0")Hi-Z54DSDL2IAudio Serial Data Input pin in Pin control mode.<br>(@DSDPATH bit = "0")Hi-Z54DSDR2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CISerial Control Interface Select pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z55I2CISerial Control Interface Select pin in Register Control<br>mode.<br>"L": 3-wire serial control interface.<br>"H": I?C Bus serial control interface.Pull-down to<br>DVSS56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                 | 40  | SSLOW    |     | Digital Filter Select pin in Pin Control mode                                                          | 11: 7               |

| 49TDMOOAudio Serial Data Output pin in Daisy Chain mode<br>(Internal pull-down pin)DVSS<br>(100 kΩ, typ)50DEM0IDe-emphasis Enable pin in Pin Control mode<br>Audio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z51DSDR1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z52TDM0ITDM Mode select 0 pin in Pin control mode.<br>(@DSDPATH bit = "0")Hi-Z53DCLKIDSD Clock pin in DSD mode (@DSDPATH bit ="0")<br>(@DSDPATH bit = "0")Hi-Z53DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DSDR2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55INVRIDaisy Chain Mode Select pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z55I2CIR1/2ch Signal Invert pin in Pin Control mode<br>(@DSDPATH bit = "0")Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48  | WCK      | I   | Word Clock input pin in EXDF mode                                                                      | HI-Z                |

| 50DSDL1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z51DSDR1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z52TDM0ITDM Mode select 0 pin in Pin control mode.<br>(@DSDPATH bit = "0")Hi-Z52DCLKIDSD Clock pin in DSD mode (@DSDPATH bit ="0")<br>(@DSDPATH bit = "0")Hi-Z53DCLKIDSD Clock pin in DSD mode (@DSDPATH bit ="0")<br>(@DSDPATH bit = "0")Hi-Z53DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DCHAINIDaisy Chain Mode Select pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z54DCHAINIDaisy Chain Mode Select pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55INVRIR1/2ch Signal Invert pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CISerial Control Interface Select pin in Register Control<br>mode.<br>"H": I <sup>2</sup> C Bus serial control interface.<br>"H": I <sup>2</sup> C Bus serial control interface.Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                               | 49  | TDMO     | 0   |                                                                                                        | DVSS                |

| DSDL1I(@DSDPATH bit = "0")51DSDR1IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z52TDM0ITDM Mode select 0 pin in Pin control mode.<br>DCLKHi-Z52DCLKIDSD Clock pin in DSD mode (@DSDPATH bit ="0")Hi-Z53DSDL2IAudio Serial Data Input pin in Pin control mode.<br>(@DSDPATH bit = "0")Hi-Z53DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DCHAINIDaisy Chain Mode Select pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z54DCHAINIDaisy Chain Mode Select pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z55INVRIR1/2ch Signal Invert pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CISerial Control Interface Select pin in Register Control<br>mode.<br>"L": 3-wire serial control interface.<br>"H": I²C Bus serial control interface.Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | DEM0     |     | De-emphasis Enable pin in Pin Control mode                                                             |                     |

| 51DSDR11(@DSDPATH bit = "0")Hi-Z52TDM0ITDM Mode select 0 pin in Pin control mode.<br>DCLKHi-Z53DCLKIDSD Clock pin in DSD mode (@DSDPATH bit ="0")Hi-Z53DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DCHAINIDaisy Chain Mode Select pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z54DSDR2IAudio Serial Data Input Pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54INVRIR1/2ch Signal Input Pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55I2CISerial Control Interface Select pin in Register Control<br>mode.<br>"H": I2C Bus serial control interface.<br>"H": I2C Bus serial control interface.<br>"H": I2C Bus serial control interface.Pull-down to<br>DVSS56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50  | DSDL1    | I   |                                                                                                        | Hi-Z                |

| 52DCLKIDSD Clock pin in DSD mode (@DSDPATH bit ="0")HI-Z53TDM1TDM Mode select 1 pin in Pin control mode.Audio Serial Data Input pin in DSD modeHi-Z53DSDL2IAudio Serial Data Input pin in DSD modeHi-Z54DCHAINIDaisy Chain Mode Select pin in Pin Control mode.Hi-Z54DSDR2IAudio Serial Data Input Pin in DSD modeHi-Z55INVRIR1/2ch Signal Invert pin in Pin Control mode.Hi-Z55I2CISerial Control Interface Select pin in Register Control<br>mode.Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51  | DSDR1    | I   |                                                                                                        | Hi-Z                |

| DCLKIDSD Clock pin in DSD mode (@DSDPATH bit = 0 )1TDM1TDM Mode select 1 pin in Pin control mode.53DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")54DCHAINIDaisy Chain Mode Select pin in Pin Control mode.54DSDR2IAudio Serial Data Input Pin in DSD mode<br>(@DSDPATH bit = "0")54IDSDR2I55INVRIR1/2ch Signal Invert pin in Pin Control mode.<br>(@DSDPATH bit = "0")55I2CISerial Control Interface Select pin in Register Control<br>mode.<br>"H": 12C Bus serial control interface.<br>"H": 12C Bus serial control interface.56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50  | TDM0     | Ι   | TDM Mode select 0 pin in Pin control mode.                                                             | Li 7                |

| 53DSDL2IAudio Serial Data Input pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z54DCHAINIDaisy Chain Mode Select pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z54DSDR2IAudio Serial Data Input Pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55INVRIR1/2ch Signal Invert pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z55I2CISerial Control Interface Select pin in Register Control<br>mode.<br>"L": 3-wire serial control interface.<br>"H": I²C Bus serial control interface.Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52  |          |     |                                                                                                        | I II-∠              |

| DSDL2(@DSDPATH bit = "0")Hit = "0")54DCHAINIDaisy Chain Mode Select pin in Pin Control mode.<br>(@DSDPATH bit = "0")Hi-Z54DSDR2IAudio Serial Data Input Pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55INVRIR1/2ch Signal Invert pin in Pin Control mode<br>Serial Control Interface Select pin in Register Control<br>mode.<br>"L": 3-wire serial control interface.Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | TDM1     |     |                                                                                                        |                     |

| 54DSDR2IAudio Serial Data Input Pin in DSD mode<br>(@DSDPATH bit = "0")Hi-Z55INVRIR1/2ch Signal Invert pin in Pin Control modeHi-Z55I2CISerial Control Interface Select pin in Register Control<br>mode.<br>"L": 3-wire serial control interface.<br>"H": I2C Bus serial control interface.Hi-Z56TESTIConnect to DVSS (Internal pull-down pin)Pull-down to<br>DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53  | DSDL2    |     |                                                                                                        | Hi-Z                |

| DSDR2     I     (@DSDPATH bit = "0")       INVR     I     R1/2ch Signal Invert pin in Pin Control mode       55     I2C     I     Serial Control Interface Select pin in Register Control mode.       I2C     I     Serial Control Interface Select pin in Register Control mode.       "L": 3-wire serial control interface.     Hi-Z       56     TEST     I       Connect to DVSS (Internal pull-down pin)     Pull-down to DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | DCHAIN   |     | Daisy Chain Mode Select pin in Pin Control mode.                                                       |                     |

| 55     I2C     I     Serial Control Interface Select pin in Register Control mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54  | DSDR2    | I   |                                                                                                        | Hi-Z                |

| 55     I2C     I     Serial Control Interface Select pin in Register Control mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55  | INVR     |     | R1/2ch Signal Invert pin in Pin Control mode                                                           |                     |

| 56 TEST I Connect to DVSS (Internal pull-down pin) DVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |          | 1   | Serial Control Interface Select pin in Register Control mode.<br>"L": 3-wire serial control interface. |                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56  | TEST     | I   | Connect to DVSS (Internal pull-down pin)                                                               |                     |

| No.     | Pin Name | I/O | Function                                                                                        | Power Down<br>State                    |

|---------|----------|-----|-------------------------------------------------------------------------------------------------|----------------------------------------|

| 57-60   | VREFHR2  | 1   | R2ch High Level Reference Voltage Input pin.                                                    | Hi-Z                                   |

| 61-64   | VREFLR2  | 1   | R2ch Low Level Reference Voltage Input pin.                                                     | Hi-Z                                   |

| 65-67   | VSSR2    | -   | R2ch Analog Ground pin.                                                                         | -                                      |

| 68-70   | VDDR2    | -   | R2ch Analog Power Supply pin.                                                                   | -                                      |

| 71      | VCOMR2   | Ι   | R2ch VCOM pin. VCOMR2 is connected to the midpoint of resistors between VREFHR2 and VREFLR2.    | Hi-Z                                   |

| 72      | EXTCR2N  | 0   | External Capacitor Connection pin. This pin should be connected to 1 $\mu F$ to VSSR2.          | Pull-down to<br>VSSR2<br>(250 kΩ, typ) |

| 73,74   | IOUTR2N  | 0   | Current Output pin (R2ch negative signal).                                                      | Connected to<br>OPINR2N<br>(64 Ω, typ) |

| 75      | OPINR2N  | 0   | Common Voltage Input pin (R2ch negative signal).                                                | Connected to<br>IOUTR2N<br>(64 Ω, typ) |

| 76      | OPINR2P  | 0   | Common Voltage Input pin (R2ch positive signal).                                                | Connected to<br>IOUTR2P<br>(64 Ω, typ) |

| 77,78   | IOUTR2P  | 0   | Current Output pin (R2ch positive signal).                                                      | Connected to<br>OPINR2P<br>(64 Ω, typ) |

| 79      | EXTCR2P  | 0   | External Capacitor connection pin. This pin should be connected to 1 $\mu F$ to VSSR2.          | Pull-down to<br>VSSR2<br>(250 kΩ, typ) |

| 80,81   | NC       | -   | No internal bonding. Connect to AVSS.                                                           | -                                      |

| 82      | EXTCL2P  | 0   | External Capacitor connection pin. This pin should be connected to 1 $\mu$ F to VSSL2.          | Pull-down to<br>VSSL2<br>(250 kΩ, typ) |

| 83,84   | IOUTL2P  | 0   | Current Output pin (L2ch positive signal).                                                      | Connected to<br>OPINL2P<br>(64 Ω, typ) |

| 85      | OPINL2P  | 0   | Common Voltage Input pin (L2ch positive signal).                                                | Connected to<br>IOUTL2P<br>(64 Ω, typ) |

| 86      | OPINL2N  | 0   | Common Voltage Input pin (L2ch negative signal).                                                | Connected to<br>IOUTL2N<br>(64 Ω, typ) |

| 87,88   | IOUTL2N  | 0   | Current Output pin (L2ch negative signal).                                                      | Connected to<br>OPINL2N<br>(64 Ω, typ) |

| 89      | EXTCL2N  | 0   | External Capacitor connection pin. This pin should be connected to 1 $\mu F$ to VSSL2.          | Pull-down to<br>VSSL2<br>(250 kΩ, typ) |

| 90      | VCOML2   | I   | L2ch VCOM pin. VCOML2 is connected to the midpoint of resistors between VREFHL2 and VREFLL2.    | Hi-Z                                   |

| 91-93   | VDDL2    | -   | L2ch Analog Power Supply pin.                                                                   | -                                      |

| 94-96   | VSSL2    | -   | L2ch Analog Ground pin.                                                                         | -                                      |

| 97-100  | VREFLL2  | I   | L2ch Low Level Reference Voltage Input pin.                                                     | Hi-Z                                   |

| 101-104 | VREFHL2  | I   | L2ch High Level Reference Voltage Input pin.                                                    | Hi-Z                                   |

| 105     | EXTR     | I   | External Resistor connection pin. This pin should be connected to 33 k $\Omega$ (±1 %) to AVSS. | Hi-Z                                   |

| 106     | AVSS     | -   | Analog Ground pin                                                                               | -                                      |

| 107     | AVDD     | -   | Clock Interface Power Supply Pin, 4.75 ~ 5.25 V                                                 | -                                      |

| No.     | Pin Name | I/O | Function                                                                                                                                            | Power Down<br>State   |

|---------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 108     | MCLK     |     | Master Clock Input pin                                                                                                                              | Hi-Z                  |

| 109     | DVDD     | 0   | (LDOE pin = "H") LDO Output pin. This pin should be<br>connected to DVSS with 1.0 $\mu$ F. This pin is<br>prohibited to connect to other devices.   | DVSS                  |

|         |          | -   | (LDOE pin = "L") 1.8 V Digital Power Supply pin                                                                                                     | -                     |

| 110     | DVSS     | -   | Digital Ground pin                                                                                                                                  | -                     |

| 111     | TVDD     | -   | Digital Power Supply pin, 3.0 V~3.6 V                                                                                                               | -                     |

| 112     | LDOE     | Ι   | Internal LDO Enable pin.<br>"L": Disable, "H": Enable                                                                                               | Hi-Z                  |

| 113     | PDN      | I   | Power-Up, Power-Down pin<br>When at "L", the AK4499 is in Power-Down mode.<br>The AK4499 must always be in Power-Down mode<br>upon supply power on. | Hi-Z<br>(PDN = "L")   |

| 114     | SMUTE    | I   | When this pin is changed to "H", Soft Mute cycle is initiated.<br>When returning to "L", Soft Mute releases.                                        | Hi-Z                  |

|         | CSN      | Ι   | Chip Select pin in 3-wire serial Register Control mode                                                                                              |                       |

|         | SD       | Ι   | Digital Filter Select pin in Pin Control mode                                                                                                       |                       |

| 115     | CCLK     | Ι   | Control Data Clock pin in 3-wire serial Register<br>Control mode                                                                                    | Hi-Z                  |

|         | SCL      | I   | Control Data Clock Input pin in I <sup>2</sup> C Bus Register<br>Control mode                                                                       |                       |

|         | SLOW     |     | Digital Filter Select pin in Pin Control mode                                                                                                       |                       |

| 116     | CDTI     | Ι   | Control Data Input pin in 3-wire serial Register<br>Control mode                                                                                    | Hi-Z                  |

|         | SDA      | I/O | Control Data Input pin in I <sup>2</sup> C Bus Register Control mode                                                                                |                       |

|         | DIF0     |     | Digital Input Format 0 pin in Pin Control mode                                                                                                      | Pull-down to          |

| 117     | DZFL     | 0   | Lch Zero Input Detect pin in Register Control mode<br>(Internal pull-down pin)                                                                      | DVSS<br>(100 kΩ, typ) |

|         | DIF1     |     | Digital Input Format 1 pin in Pin Control mode                                                                                                      | Pull-down to          |

| 118     | DZFR     | 0   | Rch Zero Input Detect pin in Register Control mode<br>(Internal pull-down pin)                                                                      | DVSS<br>(100 kΩ, typ) |

| 110     | DIF2     | Ι   | Digital Input Format 2 pin in Pin Control mode                                                                                                      |                       |

| 119     | CAD0     | I   | Chip Address 0 pin in Register Control mode                                                                                                         | Hi-Z                  |

| 120     | VTSEL    | I   | MCLK VIH/L Level Select pin.<br>VTSEL = "L"; VIH = 1.36 V, VIL = 0.34 V<br>VTSEL = "H"; VIH = 2.2 V, VIL = 0.8 V                                    | Hi-Z                  |

| 121-124 | VREFHL1  | Ι   | L1ch High Level Reference Voltage Input pin.                                                                                                        | Hi-Z                  |

| 125-128 | VREFLL1  |     | L1ch Low Level Reference Voltage Input pin.                                                                                                         | Hi-Z                  |

| -       | TAB      | -   | The TAB on the bottom surface of the package should be connected to AVSS.                                                                           | -                     |

Note 2. All input pins except internal pull-up/down pins must not be left floating.

Note 3. The AK4499 must be powered down by the PDN pin when changing Pin Control/Register Control modes by the PSN pin.

Note 4. PCM mode, DSD mode, and EXDF mode are selectable in Register Control mode.

#### IMPORTANT NOTICE —

- 0. Asahi Kasei Microdevices Corporation ("AKM") reserves the right to make changes to the information contained in this document without notice. When you consider any use or application of AKM product stipulated in this document ("Product"), please make inquiries the sales office of AKM or authorized distributors as to current status of the Products.

- 1. All information included in this document are provided only to illustrate the operation and application examples of AKM Products. AKM neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of AKM or any third party with respect to the information in this document. You are fully responsible for use of such information contained in this document in your product design or applications. AKM ASSUMES NO LIABILITY FOR ANY LOSSES INCURRED BY YOU OR THIRD PARTIES ARISING FROM THE USE OF SUCH INFORMATION IN YOUR PRODUCT DESIGN OR APPLICATIONS.

- 2. The Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact, including but not limited to, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for the above use unless specifically agreed by AKM in writing.

- 3. Though AKM works continually to improve the Product's quality and reliability, you are responsible for complying with safety standards and for providing adequate designs and safeguards for your hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of the Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption.

- 4. Do not use or otherwise make available the Product or related technology or any information contained in this document for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). When exporting the Products or related technology or any information contained in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. The Products and related technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 5. Please contact AKM sales representative for details as to environmental matters such as the RoHS compatibility of the Product. Please use the Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. AKM assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.

- 6. Resale of the Product with provisions different from the statement and/or technical features set forth in this document shall immediately void any warranty granted by AKM for the Product and shall not create or extend in any manner whatsoever, any liability of AKM.

- 7. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of AKM.

### Thank you for your access to AKM products information. More detail product information is available, please contact our sales office or authorized distributors.